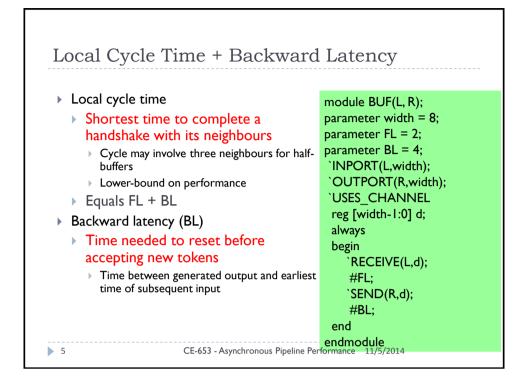

| <pre>module TOK_BUF(L, R); parameter width = 8; parameter init = 8'b0; 'INPORT(L,width); 'OUTPORT(R,width); 'USES_CHANNEL parameter FL = 2; parameter BL = 4; reg [width-1:0] d; initial begin     `SEND(R,init); end     always     begin     `RECEIVE(L,d);     #FL;     `SEND(R,d);     #BL;     end endmodule</pre> <pre>     Initial block     Mechanism to send out initial     token     Mechanism to send out     token     Mechanism     Mechanism</pre> | Token Buffer – VerilogCSP Model                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <pre>parameter width = 8; parameter init = 8'b0;<br/>`INPORT(L,width);<br/>`OUTPORT(R,width);<br/>`USES_CHANNEL<br/>parameter FL = 2; parameter BL = 4;<br/>reg [width-1:0] d;<br/>initial<br/>begin<br/>`SEND(R,init);<br/>end<br/>always<br/>begin<br/>`RECEIVE(L,d);<br/>#FL;<br/>`SEND(R,d);<br/>#BL;<br/>end</pre> | <ul> <li>Mechanism to send out initial token</li> <li>Init         <ul> <li>Value of initial token sent out</li> <li>Configurable via Verilog parameter feature</li> <li>After initial block, never used again</li> </ul> </li> <li>Always block         <ul> <li>Performs steady-state behavior</li> </ul> </li> </ul> |