| Parameter    | Was | Now     | What happened     |

|--------------|-----|---------|-------------------|

| scale factor | 1   | 1/a     |                   |

| linear size  | x   | x/a     | Dimensions shrink |

| voltage      | v   | V/a     | Reduce voltage    |

| E-field      | Е   | E       | Constant E-Field  |

| current      | i   | i/a     | Reduce current    |

| power        | vi  | vi/a^2  | Per-device        |

| delay        | т   | T/a     | Reduce delay      |

| energy       | viT | viT/a^3 |                   |

| Delay & Wire VariationBackend Computational Lithography - DFM exampleImage: Delay of the problem of the strange of the strang | <ul> <li>Wire pitch is well controlled in modern processes</li> <li>Pitch is determined by mask precision itself</li> <li>Width and space individually is not</li> <li>Width and space depend on etching and photoresist</li> </ul> |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| K Kuhn, C. Kenyon, et al. " <i>Managing Process Variation in Intel's 45 nm. CMOS Technology</i> ." Intel Technology Journal, vol. 12, no. 2, <i>Jun. 2008</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                     |  |  |  |

| ▶ 17 CE-653 - Introduction and Fu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ndamentals                                                                                                                                                                                                                          |  |  |  |

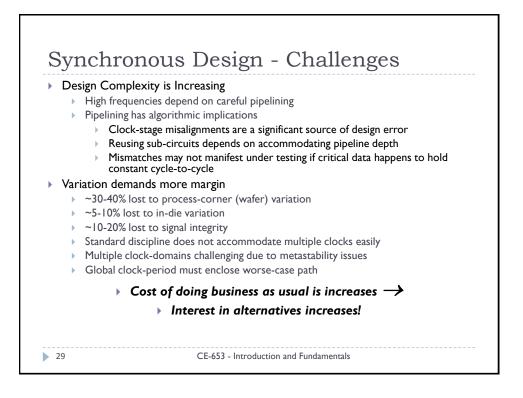

### **Baseline Analysis** Semi-Custom Synchronous Positives + Good performance/power with 12-month design times + Supported by mature CAD tools + Characterized cell library + Automated synthesis from RTL + Mature physical design flows Negatives Use constrained circuits and methodology - Static CMOS standard gates - Limited clocking and gated-clocking methodologies - Limited flip-flops with large D-Q overheads Variation in deep-submicron Timing closure problems causing schedule slips - Variability causes large margins in performance and power High electro-magnetic interference 27 CE-653 - Introduction and Fundamentals

# **Baseline** Analysis **Full-Custom Synchronous**

Positives ►

- + 2X improvement in performance and power

- + Carefully designed macro cells

- + Dynamic logic (e.g., self-resetting domino)

- + High-speed flip-flops and latches

- + Low-voltage design

- Negatives ►

28

- Increased design time (~36 months)

- Charge sharing problem with dynamic logic

- Aggressive two-sided timing assumptions

- Quality Productivity Extensive analog verification pre and post-layout

- Still may have high electro-magnetic interference

Full-custom versus semi-custom --Basic tradeoff between productivity (design-time) and quality

#### CE-653 - Introduction and Fundamentals

14

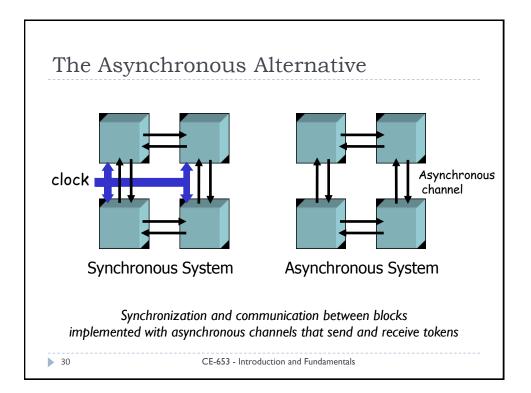

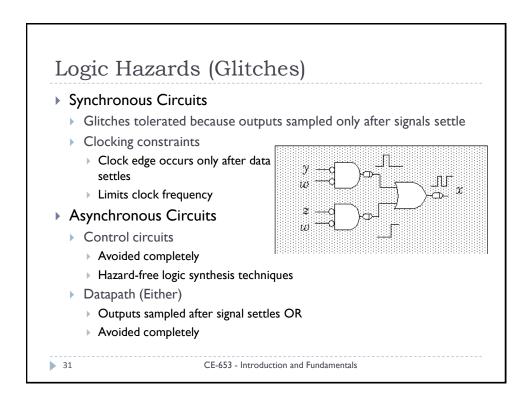

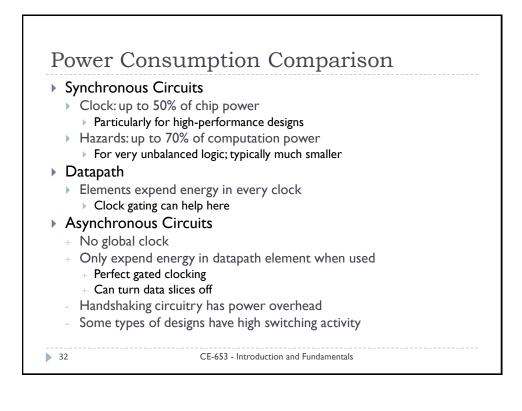

## Performance Comparison Synchronous Design Clock frequency set to worst-case conditions Semi-automated Limited circuit styles supported by automated tools Limited clocking styles and Flip-Flops/Latches Process variations lead to large over-design and limited clock frequency Full-custom Advanced circuit styles available Advanced clocking styles and latches Robustness versus performance tradeoffs Asynchronous Design Some design styles are very robust to process variations Close to full-custom performance with ASIC design times possible 33 CE-653 - Introduction and Fundamentals

# Asynchronous Challenges

### Lack of CAD tools

- Limited support from major EDA companies

- Asynchronous EDA start-up environment challenging

### High-performance asynchronous design

- > Some blocks can be 2-5x larger due to dual-rail design

- May consume more peak power than desired

- Low-power asynchronous design

- > Can be slower than desired if control overhead not managed

- Debug

- Circuit can't be slowed via clock to aid in debugging

- Asynchronous test

- Testers geared toward synchronous

- Standards do not exist and test methodologies still evolving

- Automatic test pattern generation in infancy

35

CE-653 - Introduction and Fundamentals

### Asynchronous Commercialization Efforts

### Fulcrum Microsystems (www.fulcrummicro.com)

- Fabless semi-conductor company

- High-performance computing and networking markets

- Uses high-performance async design as secret sauce

- Founded out of Caltech in 2000; Bought by Intel in 2011

- Achronix (<u>www.achronix.com</u>)

- High-performance async FPGA core with synchronous interfaces

- Founded out of Cornell research in 2006

### TimeLess Design Automation

- ASIC Flow for Asynchronous Design

- First target high-performance GHz+ silicon in 65nm

- Founded out of USC in 2008

- Sold to Fulcrum Microsystems in 2010

### Tiempo (www.tiempo-ic.com)

- IP Cores and ASIC Flow (Power/Performance Tradeoff)

- Lower performance than TimeLess Design Automation

### Numerous failed start-ups

Handshake Solutions, Silistix, Elastix, Nanochronous

#### CE-653 - Introduction and Fundamentals

36